Микроэлектроника, 2022, T. 51, № 4, стр. 265-271

Моделирование кремниевых цилиндрических с полностью охватывающим затвором КМОП нанотранзисторов с переменным радиусом рабочей области

Н. В. Масальский *

Федеральное государственное учреждение Федеральный научный центр

Научно-исследовательский институт системных исследований РАН

Москва, Россия

* E-mail: volkov@niisi.ras.ru

Поступила в редакцию 15.02.2022

После доработки 04.03.2022

Принята к публикации 10.03.2022

- EDN: YMGXAR

- DOI: 10.31857/S0544126922040081

Аннотация

Обсуждается новый кремниевый КМОП нанотранзистор с цилиндрической геометрией полностью охватывающим затвором с переменным радиусом рабочей области. Разработана 2-D аналитическая модель распределения потенциала и основанные на нем модели прямого и подпорогового токов транзистора с рабочей областью в виде усеченного конуса. Изменение геометрии транзистора по сравнению с обычной цилиндрической формой улучшает электро-физические характеристики и позволяет компенсировать ограничения возникающие в следствии масштабирования. Численные исследования конических прототипов демонстрируют улучшенные электростатические характеристики при оптимизированном отношении радиусов 0.83 по сравнению с обычной цилиндрической структурой в диапазоне управляющих напряжений от 0 до 0.6 В. Коническая структура отличается более высоким током транзистора, максимальным соотношением токов Ion/Ioff, низким током утечки и наклоном подпороговой характеристики, близким к теоретическому приделу. Таким образом, коническая архитектура с оптимизированным отношением радиусов может стать заменой цилиндрической структуры для высокоскоростных низковольтных приложений.

1. ВВЕДЕНИЕ

Кремниевой полевой КМОП транзистор с цилиндрической геометрией и полностью охватывающим затвором является одним из членов семейства gate-all-around (GAA), которое является приоритетным для современного технологического развития наноэлектроники [1]. Это эффективное решение для преодоления ограничений масштабирования планарных транзисторов и достижения высокой степени интеграции нанотранзисторных СБИС [2–4]. По мере масштабирования транзисторов уменьшение расстояния между истоком и стоком снижает управляемость затвора, нарушая классическое распределение потенциала и, тем самым ухудшая перенос носителей в рабочей области транзистора. При этом такие транзисторы характеризуются большим подпороговым током и высокой крутизной подпороговой характеристики [5–7]. Однако, дальнейшее масштабирование и усовершенствование конструкции GAA КМОП транзисторов продолжается для повышения производительности микросхем. Изменение геометрии транзистора по сравнению с его обычной формой может повысить его быстродействие и смягчить ограничения масштабирования, в частности из-за коротко-канальных эффектов (ККЭ).

В настоящей работе разработана цилиндрическая архитектура GAA нанотранзистора с переменным диаметром рабочей области. В данном случае со стороны стока она сужена по сравнению с диаметром со стороны истока и, таким образом, напоминает форму усеченного конуса. Этим приемом достигается экранировка стока, что снижает влияние горячих носителей, что, хорошо известно, приводит к повышению ток транзистора [8, 9]. Электростатические характеристики КМОП нанотранзисторов с переменным радиусом численно исследованы с помощью, разработанной в настоящей работе аналитической модели и получены оценки работоспособности рассматриваемой транзисторной структуры. Полученные результаты сравниваются с данными моделирования, выполненного с использованием 3D-симулятора TCAD Sentaurus [10].

2. СТРУКТУРА ПРОТОТИПА

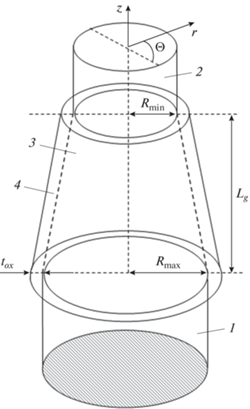

На рис. 1 показана 3D архитектура кремниевого цилиндрического с полностью охватывающим затвором КМОП нанотранзистора с коническим сечением рабочей области.

Рис. 1.

Эскиз кремниевого с полностью охватывающим затвором КМОП нанотранзистора с конической рабочей область, где 1 – исток, 2 – сток, 3 – коническая рабочая область, 4 – подзатворный диэлектрик с толщиной ${{t}_{{ox}}}$, Lg – длина рабочей области, Rmax – радиус рабочей области со стороны истока, Rmin – радиус рабочей области со стороны стока.

Хорошо известно, что при масштабировании цилиндрических транзисторных структур только уменьшение радиуса рабочей области (R) приводит к снижению тока транзистора [11]. При этом для подавления ККЭ в цилиндрической архитектуре должно выполняться условие [12, 13]:

где Lg – длина рабочей области (канала) транзистора, ${{t}_{{ox}}}$ – толщина подзатворного окисла.При этом R масштабируется проще, чем толщина подзатворного диэлектрика, которая определяет и пробойное напряжение на затворе и уровень туннельного тока затвора [12].

В настоящей работе с помощью конической конструкции снимается ограничение по параметру R. В данном случае со стороны истока для большого диаметра (или Rmax) не выполняется условие подавления ККЭ, а со стороны стока для маленького диаметра (Rmin) оно выполняется. При этом ΔR $ \ll $ Lg, где ΔR = Rmax – Rmin. Тогда из решения уравнения Пуассона можно получит распределение потенциала, вольт-амперные характеристики (ВАХ), извлечь подпороговый наклон и сделать вывод о степени влияния ККЭ в анализируемом прототипе транзистора при заданных значениях Lg, tox, Rmin/Rmax. Данную задачу мы решаем в квазиклассическом приближении зарядового разделения (ПЗР) [8, 9, 14] для минимально возможных Lg и R и низколегированной рабочей области. Это условие обеспечивает примерно равномерное распределение носителей по всему поперечному сечению рабочей области. При увеличении легирования канала потенциал носителей на его поверхности будет больше, чем в центре рабочей области. Это оттянет электроны к поверхности и приведет к ухудшению протекания тока в суживающейся части рабочей области у стока.

3. МОДЕЛЬ ПОТЕНЦИАЛА И ТОКА

Рассмотрим в рамках ПЗР задачу определения распределения потенциала в конической рабочей области рассматриваемой транзисторной структуре. В предположении, что кремниевая рабочая область транзистора однородно легирована, и влияние фиксированных окисных зарядов на ее электростатику пренебрежимо мало, то для моделирования распределения потенциала традиционно используется 2D уравнение Пуассона следующего вида [9, 12]:

(2)

$\frac{1}{r}\frac{\partial }{{\partial r}}\left( {r\frac{\partial }{{\partial r}}\varphi (r,z)} \right) + \frac{{{{\partial }^{2}}}}{{\partial {{z}^{2}}}}\varphi (r,z) = \frac{{q{{N}_{A}}}}{{{{\varepsilon }_{S}}}},$Решение уравнения Пуассона (2) ищется, используя метод, аналогичный методу Янга (параболического распределения потенциала вдоль оси z) [15], при следующих граничных условиях.

1) электрическое поле на границе затвор-окисел

2) электрическое поле в центре рабочей области

3) потенциал на краю рабочей области со стороны истока

4) потенциал на краю рабочей области со стороны стока

где $\varphi (r,z)\left| {_{{r = R{\kern 1pt} '}}} \right. = {{\varphi }_{{{{s}_{i}}}}}(z)$ – поверхностный потенциал, ${{\varepsilon }_{{ox}}}$ – диэлектрическая проницаемость подзатворного окисла, $R{\kern 1pt} '(z) = {{R}_{{\max }}} - \frac{{\Delta R}}{{{{L}_{g}}}}z$, $U_{{gs}}^{'} = {{U}_{{gs}}} - {{U}_{{FB}}}$, ${{U}_{{gs}}}$ – напряжение на затворе, ${{U}_{{FB}}}$ – напряжение плоских зон, ${{U}_{{bi}}}$ – контактная разность потенциалов, ${{U}_{{ds}}}$ – напряжение сток-исток.Следуя [9, 12] запишем решение (2) в виде

(3)

$\varphi (r,z) = {{\varphi }_{c}}(z) + \left[ {\frac{{{{\varepsilon }_{{ox}}}}}{{2R{\kern 1pt} '{{\varepsilon }_{{Si}}}}}\frac{{U_{{gs}}^{'} - {{\varphi }_{s}}(z)}}{{\ln (1 + {{t}_{{ox}}}{\text{/}}R{\kern 1pt} ')}}} \right]{{r}^{2}},$Используя известное соотношение между ${{\varphi }_{c}}(z)$ и ${{\varphi }_{s}}(z)$ в виде [12] ${{\varphi }_{c}}(z) = (1 + C){{\varphi }_{s}}(z) - CU_{{gs}}^{'}$, где $C(z) = \frac{{{{\varepsilon }_{{ox}}}}}{{2{{\varepsilon }_{{Si}}}}}\frac{1}{{\ln (1 + {{t}_{{ox}}}{\text{/}}R{\kern 1pt} ')}}$, мы преобразуем $\varphi (z,r)$ в выражение, зависящее только от ${{\varphi }_{s}}(z)$. Для получения выражения для потенциала в явном виде необходимо решить 1D уравнение Пуассона для ${{\varphi }_{s}}(z)$. Его решение можно получить аналитически при использовании вышеприведенных граничных условий. Это решение можно записать так [16]:

(4)

$\begin{gathered} {{\varphi }_{s}}(z) = \frac{1}{{\sinh \left( {\frac{{{{L}_{g}}}}{{l{\kern 1pt} '}}} \right)}} \times \\ \times \,\,\left[ {{{\Phi }_{1}}\sinh \left( {\frac{{{{L}_{g}} - z}}{{l{\kern 1pt} '}}} \right) + {{\Phi }_{2}}\sinh \left( {\frac{z}{{l{\kern 1pt} '}}} \right)} \right] - A, \\ \end{gathered} $В рамках ПЗР выражение для подпорогового тока рассматриваемого КМОП нанотранзистора по аналогии с [8, 9, 17] с учетом симметрии задачи координате $\Theta $ можно представить:

(5)

${{I}_{{ds}}} = 2\pi \frac{{{{\mu }_{{eff}}}(E)kT\left( {1 - {{e}^{{\frac{{ - q{{U}_{{ds}}}}}{{kT}}}}}} \right)}}{{\int\limits_0^{{{L}_{g}}} {\frac{{dz}}{{\pi \int\limits_0^R {{{n}_{c}}(r,z)dr} }}} }},$Зависимость подвижности от электрического поля является одним из двух основных факторов, влияющих на поведение КМОП транзистора. Она имеет очень сложную зависимость и в общем случае определяется взаимодействием четырех механизмов рассеяния [18]. Каждый из этих механизмов зависит от распределения электрического поля (E) в рабочей области. Один из наиболее широко используемых имитационных подходов сочетает в себе эти четыре компонента рассеяния в виде “эффективной подвижности” ${{\mu }_{{eff}}}(E)$ с помощью известного правила Маттиссена [19].

В режиме сильной инверсии транзистора перенос зарядов становиться более сложным. Распределение электрического поля в рассматриваемом случае отличается от простой цилиндрической геометрии. Здесь характерный размер изменений напрямую связан с величиной Rmin/Rmax. Отметим, что при умеренной концентрации легирования NA распределение носителей более равномерно по всему сечению рабочей области [20]. Это несколько снижает общий уровень напряженности электрического поля, что повышает подвижность носителей и снижает эффекты рассеяния на границе [5].

В рассматриваемом приближении общий заряд в канале транзистора n-типа состоит из подвижного (электроны) и примесного. В приближении полного обеднения ток транзистора определяется переносом подвижного заряда ${{Q}_{m}}(r,z)$ и положением квази уровня Ферми ${{V}_{n}}(r,z)$. Тогда выражение для плотности тока можно записать в виде [11]

(6)

${{i}_{{ds}}} = - 2\pi {{\mu }_{{eff}}}(E){{Q}_{m}}(r,z)\frac{{\partial {{V}_{n}}}}{{\partial z}}.$Это выражение объединяет дрейфовую и диффузную компоненты тока. В общем случае распределение зарядов можно записать так. $n = {{n}_{i}}\exp \left( { - \frac{q}{{kT}}\left( {\varphi (r,z) - {{V}_{n}}(r,z)} \right)} \right).$ Значение тока получается двойным интегрированием выражения (6).

Следует отметить, что для получения единой ВАХ зависимости (5) и (6), “сшиваются” при помощи сглаживающих функций по широко применяемому алгоритму.

4. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ И ОБСУЖДЕНИЕ

Для модельных расчетов выбран прототип КМОП нанотранзистора в соответствии с условиями приведенными в п. 1. Для данной модели длина рабочей области Lg фиксирована и составляет 25 нм. Минимальный и максимальный радиусы рабочей области выбраны 3.5 и 5 нм соответственно. Минимальное отношение Rmin/Rmax = 0.7. Исток и сток равномерно легированы примесью с концентрацией NSD = 0.5 × 1020 см−3. Концентрация легирования рабочей области NА равна 1.5 × 1015 см−3. Толщина затвора и толщина подзатворного оксида кремния tox выбраны 8 и 1.2 нм соответственно. Работа выхода металлического электрода затвора составляет 4.6 эВ.

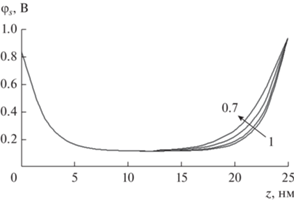

На рис. 2 показаны продольные профили поверхностного потенциала прототипов конических КМОП транзисторов с разным отношением радиусов. Они сравниваются с потенциалом классической цилиндрической геометрии при Rmin/Rmax = 1. Хорошо видно, что профили поверхностного потенциала конических прототипов со стороны стока смещены вверх (имеет большую кривизну) из-за сужения кремниевой рабочей области. Т.е. реализуется своеобразная экранировка стока, что снижает напряженность электрического поля в этой области [4, 7].

Рис. 2.

Продольные распределения поверхностного потенциала при Uds = 0.1 В в рабочей области прототипов с разными отношениями Rmin/Rmax от 1 (самая нижняя кривая) до 0.7 (самая верхняя кривая) с шагом 0.1.

Из результатов моделирования также следует, что для всех конических прототипов пик электрического поля меньше, чем для классической цилиндрической геометрии. Величина пика электрического поля минимальна для Rmin/Rmax = 0.7 и максимальена для Rmin/Rmax = 1. Такое снижение электрического поля положительным образом влияет на функционирование транзистора из-за уменьшения количества горячих носителей, о чем было отмечено выше.

Различные ключевые транзисторные характеристик были проанализированы в зависимости от величины отношения Rmin/Rmax при максимальных управляющих напряжениях.

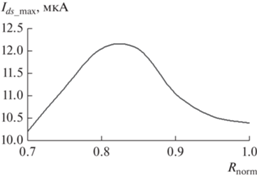

На рис. 3 приведены результаты расчетов максимального тока транзистора при разных значениях Rmin/Rmax в диапазоне 0.7–1.

Рис. 3.

Зависимость максимального тока прототипов (Ids_max) при Uds = Ugs = 0.6 В от отношения Rmin/Rmax (Rnorm).

Из рис. 3 видно, что коническая конструкция в некотором диапазоне отношения Rmin/Rmax обеспечивает больший ток стока по сравнению с обычной цилиндрической рабочей областью. Это увеличение тока стока обусловлено более равномерным распределением носителей в сечении рабочей области, которое возникает из-за сужения канала у стока. В данном случае создается наиболее благоприятные условия для транспорта носителей: отсутствие горячих носителей и высокий ускоряющий потенциал, что определяет максимально эффективный перенос носителей к стоку [2, 6, 20]. В экспериментах максимальный ток составляет 12.2 мкА при Rmin/Rmax = 0.83. По сравнению с цилиндрической рабочей областью (Rmin/Rmax = 1) максимальный ток на 1.8 мкА ниже, или меньше на 14%. Дальнейшее уменьшение Rmin/Rmax уменьшает толщину кремния, что отрицательно влияет на подвижность и токопроводимость устройства. При больших значениях отношении радиусов ток снижается из-за увеличения горячих носителей из-за ухудшения экранировки стока.

Следует отметить, что из результатов моделирования следует, что максимум проводимости также соответствует отношению Rmin/Rmax = 0.83 из-за идеальных условий транспорта носителей. Поэтому можно утверждать, что конический прототип будет иметь больший коэффициент усиления по сравнению с цилиндрическим.

Для оптимизированной транзисторной структуры рассчитаны ВАХ Ids(Uds) и Ids(Ugs), которые приведены на рис. 4. Результаты расчетов сопоставляются с данными моделирования, полученными при помощи 3D-симулятора TCAD Sentaurus.

Рис. 4.

ВАХ Ids(Uds) при Ugs = 0.6 В, где верхний – Ids(Uds) при Ugs = 0.2, 0.4, 0.6 В; нижний – Ids(Ugs) 1 — Uds = 0.05 В, 2 – Uds –0.6 В. На обоих рисунках звездочками обозначены данные моделирования TCAD.

Из сравнения можно сделать вывод о приемлемом соответствии аналитической и приборно-технологической моделей. Так при максимальных управляющих напряжениях, т.е. для максимального тока рассогласование данных составляет около 3%. При Uds = Ugs = 0.3 В ошибка составляет 5–8%. В подпороговом режиме рассогласование для тока утечки составляет примерно 15%, максимальное отклонение наблюдается для случая Uds = 0.01 В и Ugs = 0 В – около 50%. В данном случае 131 фА дает аналитическая модель и 65 фА – TCAD модель.

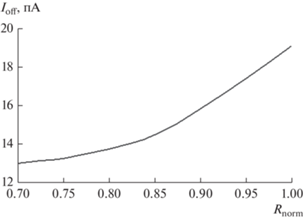

Ток Ioff играет важную роль при функционировании нанотранзистора. Этот ток уменьшает ток включения и влияет на быстродействие транзистора и микросхемы, обеспечивает ее помехозащищенность [2, 4]. Ток утечки необходимо поддерживать очень низким, чтобы уменьшить рассеивание статической мощности. Из рис. 5, где приведены результаты аналитического моделирования, можно сделать вывод, что конические прототипы обеспечивают меньший ток утечки в выключенном состоянии по сравнению с цилиндрической конструкцией.

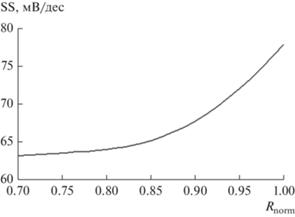

Подпороговый наклон (SS) является важным параметром для обеспечения статических и динамических характеристик коротко-канальных нанотранзисторов. В частности, чтобы получить высокое соотношение Ioff/Ion подпороговый наклон должен быть низким, близким к теоретическому приделу. На рис. 6 приведены экстрагированные значения параметра SS.

Из рис. 6 видно, что коническая конструкция имеет меньший подпороговый наклон по сравнению с цилиндрической. Для оптимизированной транзисторной структуры Rmin/Rmax = 0.83 SS = 63.7 мВ/дес. С повышением отношения Rmin/Rmax наблюдается неуклонный рост SS. После значения Rmin/Rmax = 0.86 он становится критическим. Что указывает на усиление влияния ККЭ и ограничивает диапазон возможных значений отношений Rmin/Rmax.

При разработке современных электронных устройств важно учитывать соотношение токов Ion/Ioff [12, 14]. Поэтому транзисторная структура должна обеспечивать высокое соотношение Ion/Ioff. Для оптимизированной транзисторной структуры соотношение токов составляет 6 порядков. Поэтому можно утверждать, что коническая структура характеризуется более высоким Ion/Ioff соотношением относительно классической цилиндрической.

ЗАКЛЮЧЕНИЕ

Исследована конструкция кремниевого нано размерного КМОП транзистора цилиндрической геометрии с полностью охватывающим затвором с переменным радиусом рабочей области. Рассмотрен случай когда рабочая область представляет собой усеченный конус: со стороны стока она сужена по сравнению со стороны истока. При выборе геометрии рабочей области применено условие компенсации коротко-канальных эффектов. В данном случае со стороны истока для большого диаметра не выполняется условие подавления ККЭ, а со стороны стока для маленького диаметра оно выполняется. В рамках приближения зарядового разделения разработана 2-D аналитическая модель распределения потенциала и основанные на нем модели прямого и подпорогового токов. Выбран прототип транзистора с длиной рабочей области 25 нм, большим и меньшим радиусами 5 и 3.5 нм, соответственно. В диапазоне управляющих напряжений 0–0.6 В численно исследовано поведение поверхностного потенциала, тока стока, подпорогового наклона в зависимости от значения отношения радиусов. Из результатов видно, что коническая геометрия с отношением радиусов 0.83 обеспечивает самый высокий ток стока 12.2 мА, демонстрирует максимальное соотношение Ion/Ioff ~ ~ 106 и значение крутизны подпороговой характеристики 63.7 мВ/дес. Результаты моделирования сопоставляются с данными моделирования TCAD. При этом практические во всем диапазон управляющих напряжений ошибка в среднем не превышает 15%. Полученные результаты позволяют отнести коническую структуру к высоко конкурентным в семействе GAA.

Публикация выполнена в рамках государственного задания ФГУ ФНЦ НИИСИ РАН “Проведение фундаментальных научных исследований (47 ГП)” по теме № FNEF-2021-0001 “Математическое обеспечение и инструментальные средства для моделирования, проектирования и разработки элементов сложных технических систем, программных комплексов и телекоммуникационных сетей в различных проблемно-ориентированных областях. 0580-2021-0001”, рег. № 121031300047-6.

Список литературы

International Technology Roadmap for Semiconductors (ITRS) Interconnect, 2020 Edition. [Online] Available: https://irds.ieee.org/editions/2020.

Nanoelectronics: Devices, Circuits and Systems. Editor by Brajesh Kumar Kaushik. Elsevier. 2018.

Sahay S., Kumar M. Junctionless Field-Effect Transistors: Design, Modeling, and Simulation. Wiley-IEEE Press, 2019.

Tomar G., Barwari A. Fundamental of electronic devices and circuits. Springer. 2019.

Chiang T.-K. A New Quasi-3-D Compact Threshold Voltage Model for Pi-Gate MOSFETs With the Interface Trapped Charges // IEEE Transactions on Nanotechnology. 2015. V. 14. № 3. P. 555–560.

Gao H.-W., Wang Y.-H., Chiang T.-K. A Quasi-3-D Scaling Length Model for Trapezoidal FinFET and Its Application to Subthreshold Behavior Analysis // IEEE Transactions on Nanotechnology. 2017. V. 16. № 2. P. 281–289.

Масальский Н.В. Моделирование характеристик КМОП нанотранзистора с полностью охватывающим затвором и неравномерно легированной рабочей областью // Микроэлектроника. 2019. Т. 48. № 6. С. 436–444.

Lundstrom M., Guo J. Nanoscale Transistors: Device Physics, Modeling and Simulation. Springer: New York, 2006.

Colinge J.P. FinFETs and Other Multi-Gate Transistor. NewYork: Springer-Verlag, 2008.

TCAD Sentaurus; Synopsys Inc.: Mountain View, CA, USA, 2017.

Auth C.P., Plummer J.D. Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFETs // IEEE Trans. on Electron Devices. 1997. V. 18. № 2. P. 74–76.

Ferain I., Colinge C.A., Colinge J. Multigate transistors as the future of classical metal–oxide–semiconductor field-effect transistors // Nature. 2011. V. 479. P. 310–316.

Neamen D. Semiconductor physics & devices: basic principles. New York, McGaw-Hill, 2011.

Schwierz F., Wong H., Liou J.J. Nanometer CMOS. Pan Stanford Publishing. Singapore. 2010.

Young K.K. Analysis of conduction in fully depleted SOI MOSFETs // IEEE Trans. Electron Devices, 1989. V. 36. № 3. P. 504–506.

Wang W., Liu Z., Chiang T. A New Effective-Conducting-Path-Driven Subthreshold Behavior Model for Junctionless Dual-Material Omega-Gate Nano-MOSFETs // IEEE Transactions on Nanotechnology. 2019. V. 18. № 9. P. 904–910.

He J., Chan M., Zhang X., Wang Y. A carrier-based analytic model for the undoped (lightly doped) cylindrical surrounding-gate MOSFETs // Solid State Electron. 2006. V. 50. № 3. P. 416–421.

Sze S.M. Physics of Semiconductor Device 2nd edn, John Wiley & Sons Inc.: Hoboken, New Jersey.

Iniguez B., Jimenez D., Roig J., Hamidi H.-A., Marsal L.F., Pallares J. Explicit continuous model for long-channel undoped surrounding-gate MOSFETs // IEEE Trans. Electron. Devices. 2005. V. 52. № 8. P.1868–1873.

Karthigai Pandian M., Balamurugan N.B. Analytical threshold voltage modeling of surrounding gate silicon nanowire transistors with different geometries // J. Electric Eng Technol. 2014. V. 9. № 6. P. 742–751.

Дополнительные материалы отсутствуют.

Инструменты

Микроэлектроника