#### ——— ПРИБОРЫ ——

УЛК 621.3.049.77

# ВЫСОКОВОЛЬТНЫЙ КМОП ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ ДЛЯ НИЗКОВОЛЬТОВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА

© 2022 г. В. В. Шубин\*

Новосибирский государственный технический университет, Кафедра полупроводниковых приборов и микроэлектроники, пр. К. Маркса, 20, Новосибирск, 630073 Россия \*E-mail: shubin@nzpp.ru

Поступила в редакцию 23.03.2021 г. После доработки 06.10.2021 г.

Принята к публикации 06.10.2021 г.

Представлен новый высоковольтный КМОП преобразователь уровня напряжения, предназначенный для изготовления в низко-вольтовых технологических процессах. Описаны особенности построения, работы и применения высоковольтного КМОП преобразователя, использующего низковольтные транзисторы. Проведено сравнение нового Высоковольтного КМОП преобразователя уровня напряжения с аналогом по динамическим характеристикам. Описанный Высоковольтный преобразователь уровня напряжения, по сравнению с альтернативной схемой имеет более высокое быстродействие (~14% в худшем случае), а также позволяет формировать более качественную форму выходных сигналов с минимальными искажениями.

*Ключевые слова:* преобразовательная техника, КМОП преобразователи уровня напряжения, быстродействие, качество, надежность, мощность потребления

**DOI:** 10.31857/S0544126922020089

### 1. ВВЕДЕНИЕ

Можно выделить целый ряд причин, которые определяет важность темы исследования различных преобразователей уровня напряжения:

- Необходимость сопряжения интерфейсов электронных систем с различными источниками питания.

- Согласование схем с различными уровнями напряжений внутренних сигналов.

- Снижение мощности потребления электронных систем с несколькими пороговыми напряжениями МОП транзисторов [1].

- Применение в схемах входной защиты ESD [2].

- Использование в системах с наличием режима ожидания (standby) [3].

- Применение в режиме стирания информации ячейки памяти флэш-**3У** для организации F-N туннелирования (Квантово-механический эффект туннелирования по Фаулеру—Нордхейму) и т. д. [4, 5].

Современные Системы-на-Кристалле (SoC) в силу известных причин часто требуют применения нескольких источников питания разного уровня напряжения. При этом законы масштабирования линейных размеров требуют снижения рабочих напряжений источников питания, так как уменьшение длины канала МОП транзисто-

ров приводит снижению их пробивных напряжений. Использование МОП транзисторов с повышенным пробивным напряжением в рамках одного технологического процесса требует введения новых материалов и дополнительных технологических дорогостоящих операций.

В данной статье представлен Высоковольтный КМОП преобразователь уровня напряжения, в котором за счет схемотехнических решений допускается использование стандартных низковольтных МОП транзисторов.

Предложено описание нескольких оригинальных схем высоковольтного КМОП преобразователя уровня напряжения, особенности их работы и применения, а также результаты моделирования и сравнения этих вариантов схем. В разделе 1 описан традиционный преобразователь уровня напряжения и его недостатки, в разделе 2 описана базовая схема известного высоковольтного КМОП преобразователя уровня напряжения и его работа. В разделе 3 представлены две схемы Нового высоковольтного КМОП преобразователя уровня напряжения и их отличия от базовой схемы и в разделе 4 — результаты моделирования и сравнения схем высоковольтного КМОП преобразователя уровня напряжения.

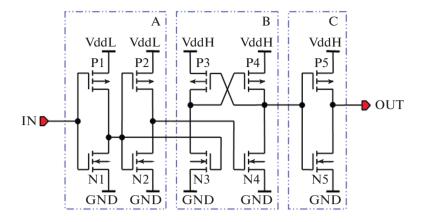

Рис. 1. 10-ти транзисторная схема Традиционного КМОП преобразователя уровня напряжения.

#### 2. ТРАДИЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ

Базовой схемой Традиционного КМОП преобразователя уровня напряжения принято называть 10-ти транзисторную схему [6—9], представленную на рис. 1.

Традиционный КМОП преобразователь уровня напряжения можно разбить на три функционально независимых блока:

- Формирователь прямого и инверсного входных сигналов низкой амплитуды (GND/VddL), выполненный на двух последовательно соединенных инверторах на транзисторах P1—P2 и N1—N2—(A).

- Преобразователь входного сигнала низкой амплитуды (GND/VddL) в сигнал высокой амплитуды (GND/VddH), построенный на триггере из двух "полу-защелок", охваченных обратной связью, на транзисторах P3—P4 и N3—N4 и запитанных от источника питания с высокой амплитуды (GND/VddH) (B).

- Выходной буфер сигнала высокой амплитуды (GND/VddH), выполненный на инверторе из КМОП транзисторов P5-N5-(C).

Иногда в качестве Формирователя прямого и инверсного входных сигналов низкой амплитуды (GND/VddL) используют один инвертор. В этом случае вход этого инвертора является входным сигналом и одновременно источником прямого сигнала, а выход — инверсного [10].

Моделирование и анализ работы схемы Традиционного КМОП преобразователя уровня напряжения помогает выявить ряд недостатков.

Для обеспечения устойчивой работы Традиционного КМОП преобразователя уровня напряжения требуется смещение передаточных характеристик вниз обеих "полу-защелок" триггера преобразователя входного сигнала низкой амплитуды (GND/VddL) в сигнал высокой амплитуды (GND/VddH). Выполнение этого условия достигается значительным уменьшением прово-

димости цепи сети подтяжки вверх на транзисторах Р3-Р4 по сравнению с проводимостью сети подтяжки вниз на транзисторах N3-N4. Данное обстоятельство в свою очередь приводит к увеличению времени переходного процесса при переключении сигнала на входе выходного буфера Традиционного КМОП преобразователя уровня напряжения из низкого уровня напряжения GND в напряжение высокого уровня VddH. Описанная особенность приводит к увеличению времени переключения формировании сигнала высокого уровня VddH на входе выходного буфера и, следовательно, к увеличению времени задержки распространения выходного сигнала низкого уровня напряжения GND на выходе Традиционного КМОП преобразователя уровня напряжения OUT. Кроме того, из-за повышенного времени переходного процесса увеличивается динамический ток потребления [11, 12].

Еще одним существенным недостатком использования Традиционного КМОП преобразователя уровня напряжения является низкая величина его рабочего напряжения вызванного ограниченными возможностями любого технологического процесса величиной пробивного напряжения МОП транзисторов. Для устранения этого недостатка используется схема, представленная в следующем разделе.

#### 3. БАЗОВАЯ СХЕМА ВЫСОКОВОЛЬТНОГО КМОП ПРЕОБРАЗОВАТЕЛЯ УРОВНЯ НАПРЯЖЕНИЯ

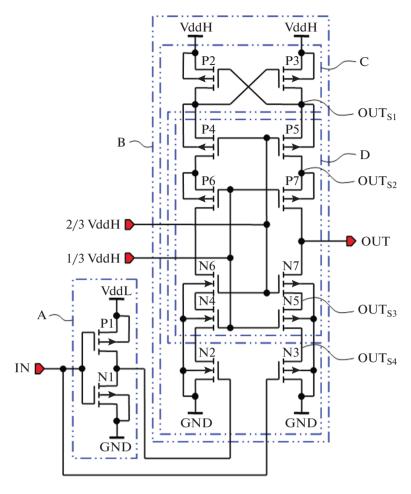

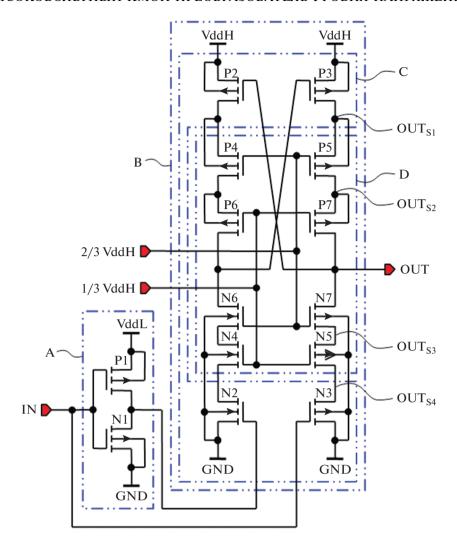

В патенте на изобретение [13] описана базовая схема высоковольтного преобразователя уровня напряжения (**БСВПУН**) и его работа. Схема этого известного устройства приведена на рис. 2. Согласно этому описанию базовая схема высоковольтного КМОП преобразователя уровня напряжения содержит два функциональных блока — "Инвертор" (A) и "Схема защелки" (B). В свою

**Рис. 2.** Базовая схема высоковольтного КМОП преобразователя уровня напряжения: A — инвертор; B — схема защелки; C — узел защелки; D — распределитель напряжения.

очередь "Схема защелки" состоит из "Узла защелки" (C) и "Распределителя напряжения" (D).

Инвертор (A) выполнен на МОП транзисторах P1 и N1 и представляет собой Генератор входного прямого и инверсного сигналов для Схемы защелки (B). Инвертор (A) запитан источником питания низкого уровня напряжения VddL и поэтому функционирует в диапазоне сигналов низкой амплитуды GND—VddL.

Сущность данного схемотехнического решения заключается в том, что в узел защелки С традиционного преобразователя уровня напряжения между транзисторами Р-типа Р2 и Р3 (Pull-Up Network) и транзисторами N-типа N2 и N3 (Pull-Down Network) введен распределитель напряжения на транзисторах Р-типа Р4—Р7 и N-типа N4—N7, образующих каскодное включение этих транзисторов. Как показывает моделирование, такое изменение схемы позволяет перераспределить напряжение высокого уровня VddH между всеми транзисторами Защелки В, таким образом, что между двумя любыми терминалами любого МОП

транзистора разница потенциалов не превышает  $\sim 1/3 \text{ VddH}$  в любом статическом режиме.

Таким образом, если технологический процесс изготовления ИС ограничен напряжением ~1/3 VddH, а на выходе схемы преобразователя уровня напряжения требуется получить напряжение VddH, то данное решение позволяет выполнить данное условие без дополнительных затрат, связанных с внесением необходимых изменений в технологический процесс для повышения его рабочего напряжения.

Кроме того, отметим еще одну полезную область применения, описанной базовой схемы Высоковольтного преобразователя уровня напряжения. В зависимости от подключения выходного терминала OUT, схема позволяет сдвигать диапазон выходного напряжения и использовать ее непосредственно как схему сдвига или как преобразователь промежуточного уровня напряжения OUT $_{\rm S3}$  и OUT $_{\rm S4}$ . На рис. 3 показан график изменения напряжений переключения БСВПУН при исполь-

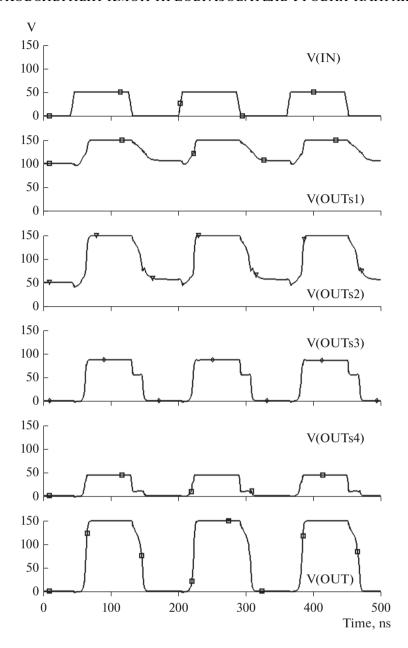

**Рис. 3.** График изменения напряжения переключения БСВПУН во времени на выходах OUT, OUT<sub>S1</sub>, OUT<sub>S2</sub>, OUT<sub>S3</sub> и OUT<sub>S4</sub> без нагрузки.

зовании выходов OUT, OUT $_{\rm S1}$ , OUT $_{\rm S2}$ , OUT $_{\rm S3}$  и OUT $_{\rm S4}$  без нагрузки.

Однако описанное решение обладает рядом недостатков:

• На выходах OUT, OUT $_{S1}$ , OUT $_{S2}$ , OUT $_{S3}$  и OUT $_{S4}$  Схемы защелки **B** БСВПУН формируются напряжения амплитудой 0–VddH, OUT $_{S1}$  – ~2/3VddH–VddH, OUT $_{S2}$  – ~1/3VddH–VddH, OUT $_{S3}$  – 0–~2/3VddH, OUT $_{S4}$  –0–~1/3VddH. Указанные приближения значений уровней отличаются от необходимых полных на величину 1–2 значения пороговых напряжений МОП тран-

зисторов. Это отличие при использовании в КМОП приложениях приводит к току потребления в статическом режиме.

- Формы выходных сигналов имеют существенные искажения в отличии от формируемых стандартными КМОП логическими вентилями.

- Использование каскодной схемы включения МОП транзисторов в Схеме защелки В БСВПУН образует цепочки последовательных транзисторов Р-типа Р2, Р4, Р6 и Р3, Р5, Р7 и N-типа N2, N4, N6 и N3, N5, N7, что ограничивает нагрузочную способность по выходу и тем самым снижает быстродействие схемы.

Рис. 4. Схема 1 нового высоковольтного КМОП преобразователя уровня напряжения. (Обозначения см. рис. 2.)

Одним из способов поднять величину нагрузочной способности по выходу является увеличение крутизны каждого отдельного МОП транзистора путем увеличения их ширины канала W в цепочке всех последовательно включенных транзисторов. Однако такой способ приводит к увеличению площади кристалла и повышает входную емкость схемы защелки (В), что опять несколько снижает общее быстродействие.

Вторым способом поднятия нагрузочной способности по выходу является буферизация схемы. Выходные буферы высокой амплитуды GND—VddH предназначены для усиления выходных сигналов при работе на большую нагрузку. Однако, этот способ требует дополнительных конструктивных или технологических усилий для их защиты от чрезмерно высоких напряжений [14], а также увеличивает площадь кристалла и в той или иной мере добавляет время на прохождение сигнала через буфер.

## 4. НОВЫЙ ВЫСОКОВОЛЬТНЫЙ КМОП ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ

Для повышения быстродействия Базового высоковольтного КМОП преобразователя уровня напряжения предложено два конструктивных решения, которые позволяют частично уменьшить перечисленные выше недостатки.

Схема 1 нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1) [15] отличается от схемы БСВПУН соединением затворов транзисторов Р-типа Р2 и Р3 Узла защелки (С). В предложенной схеме затвор транзистора Р2 соединен со стоком транзистора Р5 и подложкой и истоком транзистора Р7, а затвор транзистора Р3 соединен со стоком транзистора Р4 и подложкой и истоком транзистора Р6 Распределителя напряжения (D), как показано на рис. 4.

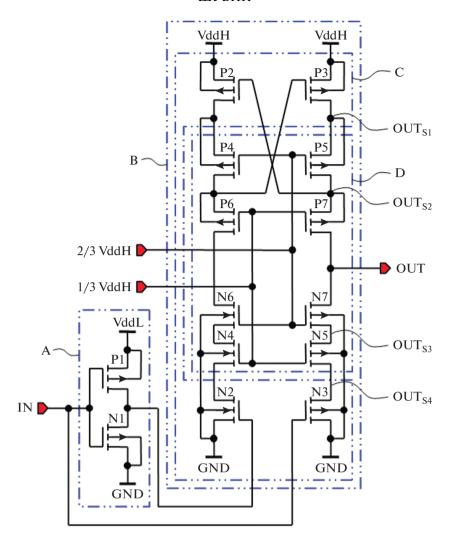

Еще одна схема 2 Нового высоковольтного КМОП преобразователя уровня напряжения

Рис. 5. Схема 2 нового высоковольтного КМОП преобразователя уровня напряжения. (Обозначения см. рис. 2.)

(НВПУН-2) [16] отличается от схем БСВПУН и НВПУН-1 соединением затворов транзисторов Р-типа Р2 и Р3 Узла защелки (С). В схеме НВПУН-2 затвор транзистора Р2 соединен со стоками транзисторов Р7 и N7, а затвор транзистора Р3 со стоками транзисторов Р6 и N6 Распределителя напряжения (D), как показано на рис. 5.

Среди ограничений характеристик технологического процесса одним из основных является максимальное (или пробивное) напряжение исток-сток МОП транзисторов в закрытом состоянии, после которого наступает пробой. Как правило, именно пробивное напряжение исток-сток определяет предельно допустимое значение рабочего напряжения технологического процесса.

Предложенное соединение помимо того, что ускоряет процесс преобразования входного сигнала, в отличие от базовой схемы, увеличивает приложенное напряжение затвор-подложка в рабочем режиме в 2—3 раза вплоть до VddH (в схеме

НВПУН-2). Однако, учитывая тот факт, что пробивное напряжение исток-сток остается неизменным, а напряжение затвор подложка в любом технологическом процессе, как правило, в несколько раз (5—10 раз) превосходит напряжение исток-сток, данное формальное изменение не оказывает негативного влияния на характеристики схемы.

# 5. РЕЗУЛЬТАТЫ МОДЕЛИРОВАНИЯ И СРАВНЕНИЯ СХЕМ ВЫСОКОВОЛЬТНОГО КМОП ПРЕОБРАЗОВАТЕЛЯ УРОВНЯ НАПРЯЖЕНИЯ

Сравнение различных принципиальных схем электронных устройств, выполняющих одинаковую функцию, представляет непростую задачу, ввиду необходимости создания равных условий для каждой из них. Поэтому для достижения более достоверных результатов необходимо принять ряд соглашений, на основании которых про-

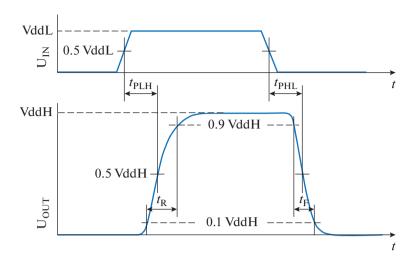

Рис. 6. Графическое представление контролируемых параметров.

водится оптимизация и сравнение. В данной работе приняты следующие соглашения:

- Длина каналов (L) всех транзисторов равна минимальному значению выбранного технологического процесса.

- Соотношение ширин каналов всех транзисторов  $W_P/W_N$  определяется согласованием их сопротивлений в открытом состоянии. Такое соотношение в КМОП вентиле обеспечивает равные передаточные характеристики при изменении входного сигнала от низкого уровня напряжения к высокому и от высокого к низкому [12].

- VddL = 5 B, VddH = 15 B.

- Высоковольтный КМОП преобразователь напряжения в диапазоне входного сигнала  $U_{IN}$  амплитудой от 0 до 5 B и выходного сигнала  $U_{OUT}$  амплитудой от 0 до 15 B.

- Длительность полных фронтов входного сигнала  $U_{\rm IN}$ , положительного  $t_R$  и отрицательного  $t_F-6$  nS.

- Емкость выходной нагрузки  $C_L 3$  pF.

- Сравнение схем проводится по результатам моделирования в равных условиях, описанных выше.

Для оценки динамических характеристик преобразования используем общепринятые параметры:

- $t_{PLH}$  и  $t_{PHL}$  времена задержек положительного и отрицательного фронтов от 0.5 значения амплитуды напряжения входного сигнала  $U_{IN}$  до 0.5 значения амплитуды напряжения выходного сигнала  $U_{OUT}$ ;

- $\mathbf{t}_R$  и  $\mathbf{t}_F$  времена длительности положительного и отрицательного фронтов выходного сигнала измеренные от 0.1 до 0.9 значения уровня амплитуды выходного сигнала.

• Цифровые значения устанавливаются выбором значений наихудшего случая в рамках единой схемы.

Перечисленные параметры представлены на рис. 6.

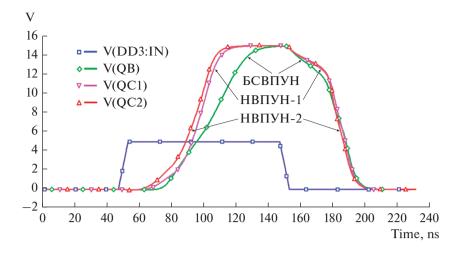

Результаты моделирования и графики получены с помощью модулей PSpice и Probe программы OrCAD 9.2 ф. Cadence, с использованием математической модели 3-го уровня и данными 3-х мкм КМОП технологического процесса. Расчеты проведены в режиме временного DC анализа "Transient" по постоянному току. На рис. 7 представлены графики результатов моделирования работы Базового (БСВПУН) и Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1, НВПУН-2).

Графики результатов моделирования наглядно демонстрируют превосходство по быстродействию Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1 и НВПУН-2) над базовой схемой (БСВПУН), а численные значения временных параметров и результаты их сравнения представлены в табл. 1. Видно ,что при сравнении значений по наихудшему случаю, которые принимаются за базовые значения при оформлении данных спецификации ТУ, любой из предложенных вариантов схем Новых высоковольтных КМОП преобразователей уровня напряжения: НВПУН-1 и НВПУН-2, превосходит по быстродействию базовую схему — БСВПУН.

Кроме того, предложенные схемы Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1 и НВПУН-2) обладают дополнительными возможностями использования в качестве схемы сдвига уровня напряжения и(или) преобразования входного сигнала до уров-

**Рис. 7.** Графики результатов моделирования работы базового (БСВПУН) и Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1, НВПУН-2), полученные с помощью модуля Probe программы OrCAD 9.2.

ня **2/3 VddH**, как показывают эпюры графиков напряжения на рис. 3.

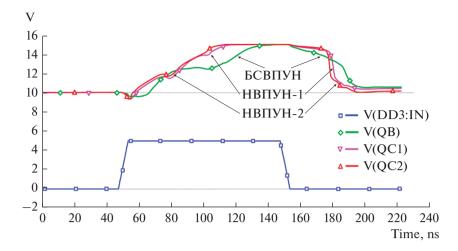

Однако при использовании Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1 и НВПУН-2) в качестве схемы сдвига, следует отметить два недостатка:

- Уровень сигнала отличается от желаемого приблизительно на величину порогового напряжения.

- Низкое качество формы фронтов, как по длительности, так и по наличию искажений формы сигналов.

Как показывают графики результатов моделирования, использование предложенных схем Нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1 и НВПУН-2) в качестве схемы сдвига помогает заметно уменьшить величину искажений формы фронтов и их длительности (рис. 8).

Увеличенная длительность фронтов уровня напряжения приводит к увеличению времени со-

стояния, в котором в схемах между источником питания высокого уровня напряжения VddH и низкого уровня напряжения GND одновременно открыты проводящие цепи P-канальных транзисторов PUN (Pull-Up Network — сеть подтяжки вверх) и N-канальных транзисторов PDN (Pull-Down Network — сеть подтяжки вниз). Такое состояние приводит к увеличению динамического тока потребления и к снижению величины рабочей частоты Базовой схемы высоковольтного КМОП преобразователя уровня напряжения (БСВПУН), по сравнению с предложенными Новыми схемами (НВПУН-1, НВПУН-2).

#### ЗАКЛЮЧЕНИЕ

В статье описаны две схемы нового высоковольтного КМОП преобразователя уровня напряжения НВПУН-1 и НВПУН-2 для низковольтового технологического процесса. Представлены их электрические принципиальные схемы,

**Таблица 1.** Численное представление результатов моделирования сравниваемых высоковольтных КМОП преобразователей уровня напряжения — БСВПУН с НВПУН-1 и НВПУН-2

| Параметр     | БСВПУН, нс | НВПУН-1, нс | НВПУН-2, нс | Превосходство НВПУН-1/НВПУН-2 над БСВПУН по быстродействию, % |

|--------------|------------|-------------|-------------|---------------------------------------------------------------|

| $t_{ m PLH}$ | 55.041     | 47.305      | 44.413      | 14.055/19.309                                                 |

| $t_{ m PHL}$ | 32.997     | 33.823      | 32.505      | -2.503/1.491                                                  |

| $t_{ m R}$   | 43.644     | 28.761      | 31.374      | 34.101/ <b>28.114</b>                                         |

| $t_{ m F}$   | 32.55      | 29.187      | 26.984      | <b>10.332</b> /17.100                                         |

**Рис. 8.** Графики результатов моделирования работы базового (БСВПУН) и нового высоковольтного КМОП преобразователя уровня напряжения (НВПУН-1, НВПУН-2) в качестве схемы сдвига, полученные с помощью модуля Probe программы OrCAD 9.2.

дано описание функционального устройства и их работы, основанной на оригинальном методе каскодного включения КМОП транзисторов.

В Новом высоковольтном КМОП преобразователе уровня напряжения НВПУН-1 и НВПУН-2 использовано соединение, при котором приложенное напряжение затвор-подложка повышается вплоть до VddH (в схеме НВПУН-2). Однако, вследствие того, что пробивное напряжение исток-сток остается неизменным, а напряжение затвор подложка в любом технологическом процессе, как правило, в несколько раз (5—10 раз) превосходит напряжение исток-сток, то данная особенность позволяет использовать предложенную схему в низко-вольтовом процессе.

Результаты моделирования демонстрируют, что динамические характеристики Нового высоковольтного КМОП преобразователя уровня напряжения для низковольтового технологического процесса превосходят аналогичные характеристики Базового высоковольтного КМОП преобразователя уровня напряжения. Время задержки переключения Нового высоковольтного КМОП преобразователя уровня напряжения

(НВПУН-1, НВПУН-2) уменьшено не менее, чем на ~14%, а длительность фронтов не менее, чем на ~28%. Кроме того, использование Нового высоковольтного КМОП преобразователя уровня напряжения НВПУН-1 и НВПУН-2 в качестве схемы сдвига, повышает качество формы выходных сигналов, приводит к снижению динамического тока потребления и увеличению рабочей частоты по сравнению с Базовой схемой высоковольтного КМОП преобразователя уровня напряжения.

#### СПИСОК ЛИТЕРАТУРЫ

- Kursun V. Multi-voltage CMOS Circuit Design / V. Kursun, E.G. Friedman, Chichester, West Sussex, John Wiley & Sons, Inc., August 2006, 242 p.

- 2. *Ker M.-D.* Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS intergrated circuit / M.-D. Ker, K.-C. Hsu // IEEE Trans. Device Mater. Reliabil. Jun. 2005. V. 5. № 2. P. 235–249.

- 3. Shibata N.A. 0.5-V 25-MHz 1-mW 256-Kb MTC-MOS/SOI SRAM for solar-power-operated portable personal digital equipment Sure write operation by using step-down negatively overdriven bitline scheme / N. Shibata, H. Kiya, S. Kurita, H. Okamoto, M. Tan'no, and T. Douseki // IEEE J. Solid-State Circuits. 2006. V. 41. № 3. P. 728—742.

- 4. Tilke A. Highly Scalable Embedded Flash Memory with Deep Trench Isolation and Novel Buried Bitline Integration for the 90-nm Node and Beyond / A. Tilke, L. Pescini, M. Stiftiner, R. Kakoschke, D. Shum, N. Chan, S. Kim, V. Hecht, K.J. Han // IEEE trans. Electron Devices. Jul. 2007. V. 54. № 7. p. 1681–1688.

- 5. Otsuka N. Circuit techniques for 1.5 V power supply flash memory / N. Otsuka, M. Horowitz // IEEE J. Solid-State Circuits. Aug. 1997. V. 32. №. 8. P. 1217–1230.

- Koo Kyoung-Hoi, Seo Jin-Ho, Ko Myeong-Lyong et al. A new level-up shifter for high speed and wide range interface in ultra deep sub-micron // IEEE International Symposium on Circuits and Systems. 2005. V. 2. P. 1063–1065.

- 7. Kumar Manoj, Arya Sandeep K., Pandey Sujata. Level Shifter Design for Low Power Applications // International journal of computer science & information Technology. Oct. 2010. V. 2. № 5. P. 124–132.

- 8. *Tan S.C., Sun X.W.* Low power CMOS level shifters by bootstrapping technique // Electron. Letter. 2002. V. 38. № 16. P. 876–878.

- 9. Zhang Bo, Liang Liping, Wang Xingjun. A new level shifter with low power in multi-voltage system // IEEE

- International Conference on Solid-State and Integrated Circuit Technology, Shanghai. 2006. P. 1857–1859.

- 10. *Gupta Sh., Kumar M.* CMOS Voltage Level-Up Shifter A Review // International J. Advances in Engineering Sciences. 2013. V. 3. № 3.

- 11. *Baker Jacob. R.* CMOS. Circuit Design, Layout, and Simultion // Published by Wiley IEEE Press, ISBN 9780470881323, 2th ed. 2005, 1139 p.

- Rabaey J.M. Digital Integrated Circuits: A Design Perspective. 2nd ed. / J.M. Rabaey, A. Chandrakasan, B. Nikolic // Englewood Cliffs., N.J., Prentice Hall. 2002, 800 p.

- 13. CMOS Digital Level Shift Circuit: Patent № US6099100A / Won Kee Lee; assignee LG Semicon Co Ltd. 8.08.2008.

- 14. Pan Dong, Li Harry W., Wilamowski Bogdan M. A Low Voltage to High Voltage Level Shifter Circuit for

- MEMS Application // IEEE Industry Microelectronics Symposium (Cat. No.03CH37488). Published 2003. Engineering Proceedings of the 15th Biennial University / Government.

- 15. Пат. 2712422 Российская Федерация, МПК Н03К 19/094 (2006.01). Высоковольтный преобразователь уровня напряжения / В.В. Шубин, А.В. Глухов, В.М. Быков, А.В. Егоркин; заявитель и патентообладатель АО "Новосибирский завод полупроводниковых приборов с ОКБ". № 20191035416; заявл. 26.02.19; опубл. 28.01.20, Бюл. № 4. 10 с.

- 16. Пат. 2702979 Российская Федерация, МПК Н03К 19/00 (2006.01). Высоковольтный преобразователь уровня напряжения / В. В. Шубин; заявитель и патентообладатель В.В. Шубин № 2019107414; заявл. 14.03.19; опубл. 14.10.19, Бюл. № 29. 9 с.