# ИЗБРАННЫЕ МАТЕРИАЛЫ КОНФЕРЕНЦИИ "ПРОБЛЕМЫ — РАЗРАБОТКИ ПЕРСПЕКТИВНЫХ МИКРО- И НАНОЭЛЕКТРОННЫХ СИСТЕМ" — ПРОЕКТИРОВАНИЕ ИНТЕГРАЛЬНЫХ СХЕМ

УДК 621.3.049.771.14

# МЕТОДЫ И АЛГОРИТМЫ ДЛЯ ЛОГИКО-ТОПОЛОГИЧЕСКОГО ПРОЕКТИРОВАНИЯ МИКРОЭЛЕКТРОННЫХ СХЕМ НА ВЕНТИЛЬНОМ И МЕЖВЕНТИЛЬНОМ УРОВНЕ ДЛЯ ПЕРСПЕКТИВНЫХ ТЕХНОЛОГИЙ С ВЕРТИКАЛЬНЫМ ЗАТВОРОМ ТРАНЗИСТОРА

© 2019 г. Г. А. Иванова<sup>1, \*</sup>, Д. И. Рыжова<sup>1, \*\*</sup>, С. В. Гаврилов<sup>1</sup>, Н. О. Васильев<sup>1</sup>, А. Л. Стемпковский<sup>1</sup>

<sup>1</sup>Институт проблем проектирования в микроэлектронике Российской АН ул. Советская, 3, Зеленоград, Москва, 124365 Россия

\*E-mail: ivanova\_g@ippm.ru \*\*E-mail: ryzhova\_d@ippm.ru Поступила в редакцию 20.11.2018 г. После доработки 03.12.2018 г. Принята к публикации 03.12.2018 г.

С увеличением степени интеграции микроэлектронных систем и уменьшением технологических размеров базовых элементов до 32 нм и ниже в значительной степени усложнились технологические правила и нормы проектирования. Количество правил проектирования для технологий с размерами транзистора 32 нм и ниже составляет несколько тысяч ограничений. Соблюдение полного набора правил и норм проектирования в автоматическом режиме становится невозможным при использовании существующих подходов к решению задач логического и топологического синтеза. Это ведет к необходимости большого объема ручной работы с редактированием схемы и топологии на заключительном этапе верификации проекта в целом. Переход к использованию регулярных структур в нижних слоях топологии позволил решить проблемы возрастающего числа проектных норм для технологий 22 нм и ниже. В данной работе предлагаются методы и алгоритмы для логико-топологического проектирования микроэлектронных схем на вентильном и межвентильном уровне для перспективных технологий с вертикальным затвором транзистора. Предложен метод межвентильного ресинтеза схем с учетом специфики проектирования схем на Fin FET транзисторах. Предлагаемый подход сочетает в себе методы логического реснитеза и структурной оптимизации схемы с целью достижения требуемых параметров (плошади, сбоеустойчивости или учета конструктивных особенностей СБИС). Предложен алгоритм совмещения фрагментов топологии стандартных ячеек и блоков, полученных в результате межвентильного ресинтеза с учетом специфики проектирования схем на FinFET транзисторах.

**DOI:** 10.1134/S0544126919030062

# введение

FinFET транзистор представляет собой трехмерную структуру с затвором в форме плавника. За счет такой формы повышается эффективная ширина затвора при сходной площади логической ячейки [1]. При этом значительно усложняется процесс автоматизации проектирования и верификации на соблюдение правил проектирования топологии FinFET схем. К примеру, количество таких правил в технологическом файле достигает нескольких десятков тысяч, что в сотни раз больше, чем для технологии 65 нм. Поэтому использование топологических шаблонов (как правило, регулярных) в алгоритмах автоматизи-

рованного синтеза упрощает технологию создания и верификации итоговой топологии.

Важную роль в современных САПР играют алгоритмы оптимизации таких характеристик, как занимаемая площадь, потребляемая мощность, быстродействие. Для того чтобы достичь требуемых значений по параметрам мощности, быстродействия и площади, разрабатываются новые более эффективные алгоритмы структурной и параметрической оптимизации в маршруте автоматизированного проектирования ИС. Такие алгоритмы, как правило, состоят из следующих этапов: логическая оптимизация системы булевых функций [3—5], оптимизация принципиальных схем [7] и топологическая оптимизация.

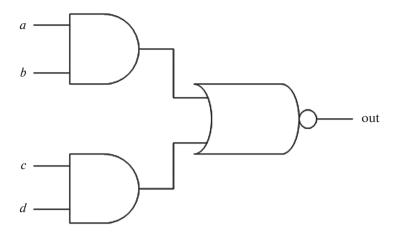

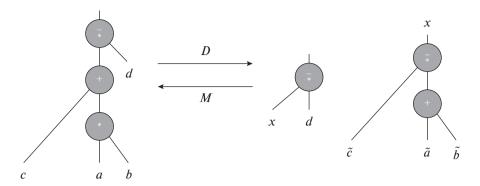

Рис. 1. Описание вентиля АОІ22 на логическом уровне.

Предлагаемый в работе подход к оптимизации состоит из двух связанных воедино этапов, которые поочередно выполняются в цикле оптимизации. На первом этапе происходит оптимизация булевых функций и принципиальной схемы. Следом за этим происходит топологическая оптимизация.

### ГРАФОВАЯ МОДЕЛЬ

В основе предлагаемого подхода лежит известная модель на основе графа вложенности после-

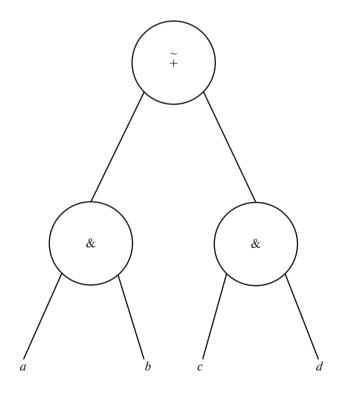

Рис. 2. Графовая модель вентиля АОІ22.

довательно-параллельных структур [1-3]. Для логического описания схемы используются следующие функции: конъюнкция для последовательного соединения внутри вентиля (f(a, b) = a & b), дизъюнкция для параллельного соединения внутри вентиля (f(a, b) = a + b), отрицание (f(a) = a), конъюнкция с отрицанием для последовательного соединения на выходе вентиля ( $f(a, b) = \sim (a \& b)$ ), дизъюнкция с отрицанием для параллельного соединения на выходе вентиля  $(f(a, b) = \sim (a + b))$ . Данную систему логических функций можно описать в виде ациклического графа, в котором вершины соответствуют логическим функциям, а дуги – ссылкам на аргументы функций (рис. 1, 2). Причем, несмотря на то, что логические операции обладают коммутативностью, порядок дуг будет иметь значение в дальнейшем. Поэтому граф является упорядоченным.

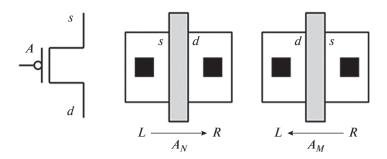

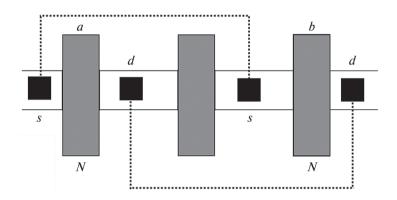

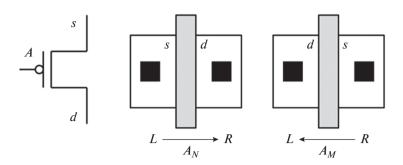

В разработанном алгоритме предусмотрен выбор физической ориентации транзисторов. Если направление слева направо соответствуют направлению от истока к стоку, то транзистор находится в нормальной ориентации. Если направление слева направо соответствует направлению от стока к истоку, то транзистор находится в зеркальной ориентации (рис. 3).

Выбор топологической ориентации транзисторов в эскизе топологии позволяет уменьшить итоговую площадь схемы за счет сокращения количества изолирующих затворов [6].

## АЛГОРИТМ СТРУКТУРНОЙ ОПТИМИЗАЦИИ

Для решения проблемы реструктуризации схем требуется алгоритм сравнения подграфов. Есть два варианта решения данной проблемы: логический и структурный. Логический (например, сравнение BDD) обеспечивает проверку эквивалентности логических функций, но является до-

**Рис. 3.** Ориентации транзистора (N — нормальная ориентация, M — зеркальная ориентация).

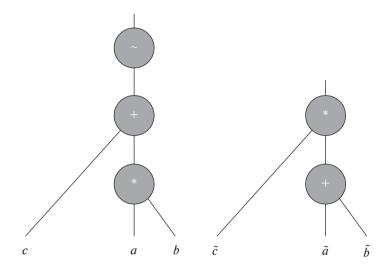

Рис. 4. Замена вентиля комплементарным.

статочно медленным, так как требуется проверка n! комбинаций, где n- количество входов. Структурный подход позволяет проверить изоморфизм графов схемы с точностью до перестановок. Эквивалентность в структурном плане является достаточным, но не необходимым условием логической эквивалентности. Структурный подход является более быстрым, но для обеспечения того, чтобы структурная эквивалентность была также и

необходимым условием, требуется отсутствие повторяющихся входов. В работе используется алгоритм, комбинирующий оба подхода. Структурное сравнение используется рекурсивно внутри логического сравнения в случае отсутствия повторяющихся входов.

Целевая функция алгоритма структурной оптимизации имеет следующий вид:

$$F_{\cos t}(G) = k_A \frac{A}{A_0} + (1 - k_A) \frac{P}{P_0} + k_{\text{Dex}} \frac{D_{\text{ex}}}{D_0} + k_{\text{Dmax}} \frac{D_{\text{max}}}{D_0} + k_{\text{nLG}} N_{\text{nLG}},$$

где A — суммарная площадь, P — суммарная мощность,  $D_{\rm ex}$  — суммарное превышение норм по задержкам для первичных выходов,  $D_{\rm max}$  — максимальное превышение нормы по задержке среди первичных выходов,  $N_{\rm nLG}$  — количество не библиотечных элементов,  $A_0$  — начальная площадь,  $P_0$  — начальная мощность,  $D_0$  — задержка минимального инвертора,  $k_A$ ,  $k_{\rm Dex}$ ,  $k_{\rm Dmax}$ ,  $k_{\rm nLG}$  — коэффициенты, которые задают приоритет составных частей целевой функции.

Логическая оптимизация строится на законах булевой алгебры. В работе используются следующие виды логических преобразований:

- Преобразования де Моргана (рис. 4) [7];

- Декомпозиция вентиля (рис. 5) [8];

- Слияние вентилей (рис. 5) [9];

- Вставка и удаление буфера [10].

**Рис. 5.** Декомпозиция (D) и слияние (M).

Рис. 6. Транзисторы находятся в нормальной ориентации.

### ТОПОЛОГИЧЕСКАЯ ОПТИМИЗАЦИЯ

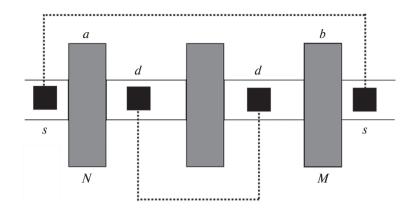

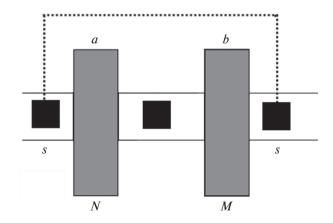

Изолирующий затвор между двумя рядом расположенными транзисторами можно удалить, если два контакта, расположенных по разные стороны от изолирующего затвора, подключены к одному узлу [11]. Например, на рис. 6 два транзистора подключены параллельно, оба транзистора находятся в нормальной ориентации. В таком случае убрать изолирующий затвор нельзя, так как контакты, находящиеся по обе стороны от него, подключены к разным узлам. Но если у одного из транзисторов изменить ориентацию на зеркальную, как это сделано на рис. 7, то можно будет избавиться от изолирующего затвора и одного из контактов и получить более компактный эскиз топологии (рис. 8).

Для получения оптимального варианта используются два метода. Первый используется, если количество входов в вентиле меньше заданного числа, и заключается в полном переборе всех возможный вариантов. Всего будет возможно  $n!(2^n+2^n)$  вариантов, где n — число входов вентиля, n! — число возможных перестановок транзисторов,  $2^n$  — число возможных вариантов ориентаций транзисторов. В таком случае обеспечивается наилучшее решение. Но в связи с тем, что n!

возрастает очень быстро, то с увеличением числа входов в вентиле требуется достаточно много ресурсов для полного перебора.

В связи с этим, если количество входов превышает определенное число, то решение ищется с помощью эвристического подхода, суть которого сводится к тому, чтобы найти два транзистора, у которых два контакта подключены к одному узлу, и поставить их рядом, повернув их в наиболее подходящие ориентации.

# АЛГОРИТМ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ ТОПОЛОГИИ FINFET CXEM

Для процесса автоматизации проектирования цифровых схем на FinFET транзисторах, изготавливающихся по техпроцессу 32 нм и ниже, на ранних этапах характерно использование алгоритмов автоматического синтеза эскизной топологии без учета межсоединений [13]. Разработанный маршрут топологического проектирования включает следующие этапы:

1. На первом этапе обрабатывается описание схемы после логического синтеза (или ресинтеза) — определяется набор шаблонов для последовательно-параллельных цепочек транзисторов

**Рис. 7.** Транзистор a находится в нормальной ориентации, транзистор b — в зеркальной. Изолирующий затвор можно удалить.

*p*- и *n*-типа (подсхем), которые будут задействованы, и набор связей этих подсхем друг с другом.

- 2. На втором этапе создаются шаблоны топологии выбранных подсхем.

- 3. На третьем этапе задействуются механизмы склейки шаблонов топологии, причем для больших схем (сотни-тысячи вентилей) производится предварительная кластеризация подсхем в блоки [14, 15].

- 4. На заключительном этапе происходит трассировка соединений между шаблонами в полуручном режиме.

На начальном этапе схема устройства разбивается на более простые подсхемы, которые могут быть описаны одним из вариантов булевой функции:

- 1.A + B

- 2. AB

- 3. A + B + C

- 4.A + BC

- 5. ABC

- 6. A(B + C)

- 7. A + B + C + D

- 8. A + B + CD

- 9.A + BCD

- 10. ABCD

- 11. A(B + C + D)

- 12. AB(C + D)

- 13. AB + CD

- 14. A(BC + D)

- 15. A + B(C + D)

- 16. (A + B)(C + D)

Далее проектируются топологические шаблоны. При разработке шаблонов количество функциональных затворов ограничивалось четырьмя, дальнейшее увеличение количества шаблонов приводит к значительному усложнению задачи. Для выбранных булевых функций строятся ком-

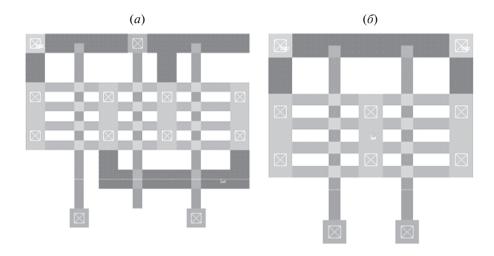

пактные шаблоны топологии с регулярностью в слоях диффузии и поликремния, минимизация площади шаблонов происходит за счет выбора ориентации каждого отдельного транзистора (рис. 9). Ориентация транзистора считается нормальной (N), если исток транзистора располагается слева, а сток — справа. Соответственно, для реализации зеркальной ориентации (M) сток и исток меняются местами.

В результате выбора оптимальной ориентации появляется возможность объединения областей диффузии соседних транзисторов и удаления изолирующего затвора (рис. 10).

Стоит заметить, что после слияния областей диффузии в последовательном соединении транзисторов отпадает необходимость в проектировании контактов к объединенной области, что, в свою очередь, упрощает последующую трассировку.

Относительную площадь итоговой топологии можно представить в виде следующего формульного выражения:

Рис 8. Удаление изолирующего затвора.

Рис. 9. Ориентация транзистора.

**Рис. 10.** Топология параллельного соединения p-транзисторов: (a) оба транзистора в нормальной ориентации, ( $\delta$ ) один транзистор в нормальной ориентации, второй — в зеркальной.

$$W_{\text{топ}} = Na + (N-1)b - Ke,$$

$a = L_{\text{тран}} + 2\text{con} + 2\text{rule},$

$b = L_{\text{тран}} + 2\text{rule},$

$e = L_{\text{тран}} + 2\text{rule} + \text{con},$

где N — количество транзисторов, K — количество удаленных затворов, a — размер транзистора, b — размер изолирующего затвора, e — размер удаленного затвора, соп — размер контакта, rule — DRC правило отступа слоя поликремния от области контакта.

Полученные шаблоны можно соединять друг с другом, причем часть объединений не требует изолирующего затвора. Это возможно, когда находящаяся на месте стыка область одного шаблона является входным узлом, а присоединяемая область другого — выходным для создания последовательного соединения. Для параллельного соединения оба шаблона должны иметь одинаковую область на месте стыка. При соединении проводится перепроверка межсоединений/под-

ключений к питанию, удаление лишних соединений.

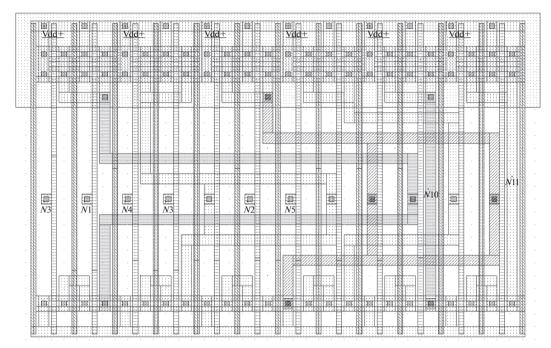

Пример работы алгоритма склейки шаблонов для схемы с17 из набора ISCAS85 приведен на рис. 11-12.

Часть использованных шаблонов выделена прямоугольниками. Пересечения прямоугольников обозначают места склейки шаблонов, не требующие изолирующего затвора. Количество изолирующих затворов сократилось в 11/2 = 5.5 раз (без учета затворов, ограничивающих всю схему).

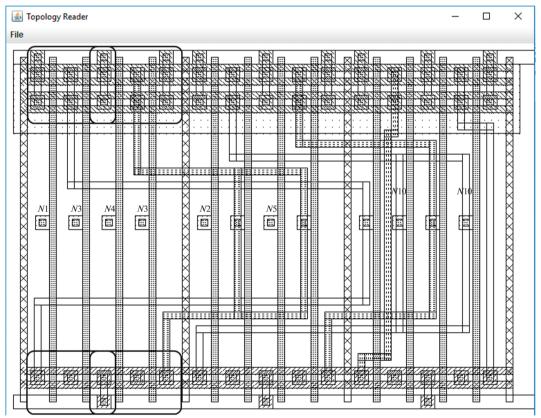

### ОПИСАНИЕ РАЗРАБОТАННОЙ ПРОГРАММЫ

На вход программы подается схемотехническое описание схемы. Данное описание экстраги-

Рис. 11. Топология схемы с 17, все транзисторы с нормальной ориентацией.

Рис. 12. Компактная топология схемы с17 после склейки.

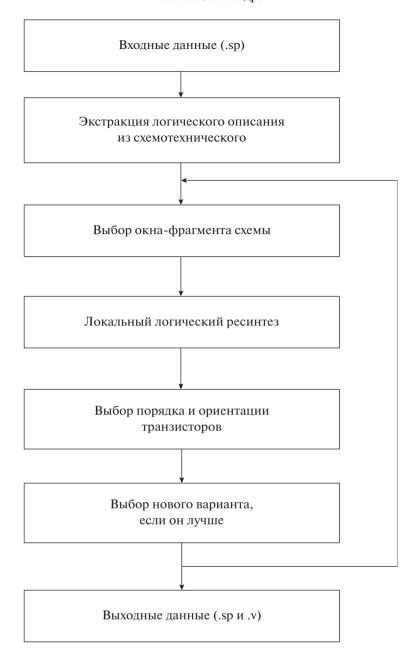

руется в логическое. Алгоритм ресинтеза не рассматривает всю схему целиком, а выбирает фрагмент схемы, с которым будет проводиться оптимизация на данном этапе (данный фрагмент называется "окном"). На следующем шаге происходит логический ресинтез в окне. После этого полученное логическое описание экстрагируется в транзисторное описание для выбора оптималь-

Рис. 13. Последовательность действий.

ных расположений и ориентаций транзисторов в вентилях. Затем новый вариант сравнивается со старым. Выходными данными программы являются SPICE-описание и Verilog-описание ресинтезированной схемы.

Общая последовательность действий изображена на рис. 13.

### РЕЗУЛЬТАТЫ

Численные эксперименты, подтверждающие эффективность разработанных методов и алгоритмов, проводились с использованием тестовых

схем из стандартных наборов. Тестирование проводилось в двух режимах: в первом происходила структурная оптимизация (табл. 1), во втором добавлялась топологическая оптимизация (табл. 2).

Структурная оптимизация проводилась дважды: в первый раз не было ограничения на процент деградации задержки, во втором осуществлялся контроль превышения норм задержки. Максимальный допустимый процент деградации задержки при оптимизации равен 10%.

За счет структурной оптимизации на больших схемах возможно уменьшение количества транзисторов на 30–50% при контроле быстродей-

Таблица 1. Результаты работы программы

| Схема | Уменьшение количества транзисторов при логическом ресинтезе, % | Общее уменьшение площади, % | Дополнительное уменьшение площади за счет расстановки транзисторов, % |

|-------|----------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------|

| C1355 | 39.86                                                          | 47.63                       | 7.77                                                                  |

| C1908 | 54.11                                                          | 59.75                       | 5.64                                                                  |

| Cnt_0 | 20.24                                                          | 30.00                       | 9.76                                                                  |

| Cnt_1 | 22.86                                                          | 32.23                       | 9.37                                                                  |

| Cla   | 28.57                                                          | 37.62                       | 9.05                                                                  |

| c17   | 8.33                                                           | 16.67                       | 8.34                                                                  |

Таблица 2. Результаты работы программы

| Схема | Начальное количество изолирующих затворов | Количество изолирующих затворов после топологической оптимизации |

|-------|-------------------------------------------|------------------------------------------------------------------|

| C1355 | 725                                       | 266                                                              |

| C1908 | 830                                       | 305                                                              |

| Cnt_0 | 133                                       | 56                                                               |

| Cnt_1 | 134                                       | 53                                                               |

| Cla   | 359                                       | 149                                                              |

| c17   | 10                                        | 4                                                                |

ствия. За счет выбора порядка и ориентации транзисторов можно улучшить полученный результат в среднем еще на 8%.

### ЗАКЛЮЧЕНИЕ

В работе был предложен метод ресинтеза микроэлектронных схем, применяющий два подхода.

Первый подход направлен на минимизацию площади с помощью оптимизации логической функции. Для этого подхода была разработана графовая модель, описывающая логическую функцию схемы. Благодаря булевой форме графа удается сохранить достаточное количество степеней свободы.

Второй подход оптимизирует топологическую структур схемы. Кроме дополнительного выигрыша по площади, это обеспечивает упрощение автоматизации синтеза топологии.

В результате был получен алгоритм, в котором последовательно выполняются эти подходы внутри цикла оптимизации. Он был протестирован на наборе стандартных тестовых схем. В ходе этого эксперимента были получены результаты, подтверждающие его эффективность. В среднем, выигрыш по площади на данном наборе схем составил 37%.

Кроме того, алгоритм межвентильного ресинтеза уже зарекомендовал себя как эффективный и быстрый в области проектирования блоков и элементов на перспективных FinFET технологиях [12].

В перспективе планируется провести сравнение результатов разработанных методов и алгоритмов с существующими аналогами по параметрам сбоеустойчивости и эффективности размещения элементов в базисе ПЛИС с иерархической архитектурой.

### СПИСОК ЛИТЕРАТУРЫ

- 1. Гаврилов С.В., Иванова Г.А., Манукян А.А. Методы проектирования заказных сложно-функциональных блоков в базисе элементов с регулярной топологической структурой в слоях поликремния и диффузии // VI Всероссийская научно-техническая конференция "Проблемы разработки перспективных микро- и наноэлектронных систем 2014". Сб. тр. под общ. ред. академика РАН А.Л. Стемпковского. М.: ИППМ РАН, 2014. Часть І. С. 161—166.

- 2. *Bryant R.E.* Graph-Based Algorithms for Boolean Function Manipulation // IEEE Transactions on Computers. 1986. P. 677–691.

- 3. *Гаврилов С.В., Гудкова О.Н., Щелоков А.Н.* Логиковременной анализ нанометровых схем на основе интервального подхода. // Известия ЮФУ. Технические науки. 2012. № 7(132). С. 85—91.

- 4. *Гаврилов С.В.* Методы анализа логических корреляций для САПР цифровых КМОП СБИС. М.: Техносфера, 2011. 136 с.

- 5. Гаврилов С.В., Глебов А.Л., Стемпковский А.Л. Методы логического и логико-временного анализа цифровых КМОП СБИС. М.: Наука, 2007. 223 с.

- 6. Гаврилов С.В., Карева Е.С., Рыжова Д.И. Разработка алгоритмов логико-топологического синтеза

- библиотечных элементов и блоков с регулярной структурой для технологических норм проектирования 32 нм // Известия ВУЗов. Электроника. 2017. Т. 22. № 4. С. 369-378.

- 7. *Уилкинсон Б*. Основы проектирования цифровых схем. Издательский дом Вильямс, 2004. 320 с.

- 8. Gavrilov S.V., Glebov A.L., Pullela S., Moore S., Vijayan G., Dharchoudhury A., Rajendran Panda, Blaauw D. Library-Less Synthesis for Static CMOS Combinational Logic Circuits // Proceedings ICCAD-97. 1997, San Jose, CA. P. 658–662.

- Gavrilov S.V., Glebov A.L. BDD-based circuit level structural optimization for digital CMOS // 1-st Intern. Workshop "Multi-Architecture Low Power Design". 1999. P. 45–49.

- Turgis S., Azemad N., Auvergne D. Design and Selection of Buffers for Minimum Power-Delay Product // ED&TC-96. P. 224–228.

- 11. Гаврилов С.В., Карева Е.С., Рыжова Д.И., Щелоков А.Н. Методы разработки графовых моделей регулярных структур FinFET транзисторов с незави-

- симыми затворами // Известия ЮФУ. Технические науки. 2017. № 7(192). С. 175—185.

- Gavrilov S., Ryzhova D., Vasilyev N. Models and methods of inter-gate resynthesis at the transistor level for nanoelectronic circuits based on FinFETs // 2018 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus). 2018. P. 1364–1367.

- 13. Kushwah R.S., Chauhan M., Shrivastava P., Akashe Sh. Modelling and Simulation of FinFET Circuits with Predictive Technology Models // Radioelectronics and Communications Systems. 2014. V. 57. № 12. P. 553–558.

- Li J., Behjat L., Schiffner B. A structure based clustering algorithm with applications to VLSI physical design // System-on-Chip for Real-Time Applications, 2005. Proceedings. Fifth International Workshop on, 20–24 July 2005. doi 10.1109/IWSOC.2005.29

- 15. *Manikandan R*. Effective Clustering Algorithms for VLSI Circuit Partitioning Problems // Contemporary Engineering Sciences, August 2014. № 7(19). P. 923–929. doi 10.12988/ces.2014.465